#### CFP2-WDM-DETS-1HL-OPC

Cisco® CFP2-WDM-DETS-1HL Compatible TAA Compliant 100GBase-DCO CFP2 Transceiver (SMF, 1528.77nm to 1568.36nm, 80km, LC, TOF)

#### **Features**

- CFP Multi-Source Agreement Compliant

- Hot pluggable CFP2 footprint

- Supports CAUI-4 for 100GE and CEI-28G-VSR for OTU4 Host Interface

- Proprietary Internal Soft-Decision Forward Error Correction (SD-FEC)

- Single-mode Fiber

- Tunable C-band Transmitter

- Tunable Optical Filter (TOF)

- Coherent Receiver

- Single-mode Fibre

- Operating temperature range 0C to 70C

- Power Consumption < 19W

- Single +3.3V Power Supply

- 100GBase Ethernet

- Access and Enterprise

### **Product Description**

This Cisco® CFP2-WDM-DETS-1HL compatible CFP2 transceiver provides 200GBase-DWDM throughput up to 80km over single-mode fiber (SMF) using a wavelength of 1528.77nm to 1568.36nm via an LC connector. It is guaranteed to be 100% compatible with the equivalent Cisco® transceiver. This easy to install, hot swappable transceiver has been programmed, uniquely serialized and data-traffic and application tested to ensure that it will initialize and perform identically. It is built to meet or exceed the specifications of Cisco®, as well as to comply with MSA (Multi-Source Agreement) standards to ensure seamless network integration. This transceiver is Trade Agreements Act (TAA) compliant. We stand behind the quality of our products and proudly offer a limited lifetime warranty.

OptioConnect's transceivers are RoHS compliant and lead-free.

TAA refers to the Trade Agreements Act (19 U.S.C. & 2501-2581), which is intended to foster fair and open internaltional trade. TAA requires that the U.S. Government may acquire only "U.S.-made or designated country end products.")

**Absolute Maximum Ratings**

| Parameter                          | Symbol | Min. | Тур.    | Max. | Unit | Notes |

|------------------------------------|--------|------|---------|------|------|-------|

| Storage Temperature                | Ts     | -40  |         | 85   | °C   |       |

| Operating Case Temperature         | Тс     | 0    |         | 70   | °C   |       |

| Relative Humidity (non-condensing) | RH     |      |         | 85   | %    |       |

| Compared Heat Completions          |        |      | 103.125 |      | Gbps | 1     |

| Supported Host Signal Types        |        |      | 111.81  |      | Gbps | 2     |

# Note:

- 1. 100GE as per IEEE 802.3ba. The line format can be selected as OTU4 (G.709 HD-FEC) or with SD-FEC (proprietary)

- 2. OTU4 as per ITU-T G.709. The line format can be selected as OTU4 (transparent) or with S-DFEC (proprietary)

# **Electrical Characteristics**

| Parameter            | Symbol | Min. | Тур. | Max. | Unit | Notes |

|----------------------|--------|------|------|------|------|-------|

| Power Supply Voltage | Vcc    | 3.2  | 3.3  | 3.4  | V    |       |

| Power Supply Current | Icc    |      |      | 6    | Α    |       |

| Power Dissipation    | PD     |      |      | 19   | W    |       |

## **Optical Characteristics**

| Parameter                           | Min.    | Тур. | Max.    | Unit     | Notes |

|-------------------------------------|---------|------|---------|----------|-------|

| Transmitter                         |         |      |         |          |       |

| Average Output Power                | -15     |      | 1       | dBm      | 1, 2  |

| Output Power Accuracy and Stability | -1      |      | 1       | dB       | 2, 3  |

| Centre Wavelength Range             | 1528.77 |      | 1567.54 | nm       |       |

| Frequency Grid Setting              |         | 50   |         | GHz      | 4     |

| Centre Wavelength                   | λΤ -15  | λΤ   | λΤ +15  | pm       | 4     |

| Receiver                            |         |      |         |          |       |

| Receiver Operating Wavelength       | 1528.77 |      | 1567.54 | nm       |       |

| Receiver Input Power Range          | -18     |      | 0       | dBm      | 5     |

| Receiver Sensitivity                |         |      | -25     | dBm      | 6     |

|                                     |         | 11.5 |         | dB/0.1nm | 7, 8  |

| OSNR Tolerance                      |         | 17   |         | dB/0.1nm | 7, 9  |

|                                     |         | 20   |         | dB/0.1nm | 7, 10 |

| Charactic Dispussion Tolerance      |         |      | 40      | ns/nm    | 8     |

| Chromatic Dispersion Tolerance      |         |      | 20      | ns/nm    | 9, 10 |

### **Notes:**

- 1. The output power is settable in steps of 0.1 dB within the specified wavelength range

- 2. Output power coupled into a 9/125 μm single mode fibre

- 3. Difference between the set value and actual value

- 4. Per ITU-T G.694.1 grid definition

- 5. An input power in this range guarantees optimum OSNR performance

- 6. Minimum input power needed to achieve post-FEC BER  $\leq$  10<sup>-15</sup> (OSNR > 35dB, SD-FEC enabled)

- 7. Post-FEC BER  $\leq 10^{-15}$ , SD-FEC enabled

- 8. 100G QPSK, post-FEC BER  $\leq 10^{-15}$ , SD-FEC enabled

- 9. 200G 8QAM, post-FEC BER < 10-15, SD-FEC enabled

- 10. 200G 16QAM, post-FEC BER < 10<sup>-15</sup>, SD-FEC enabled

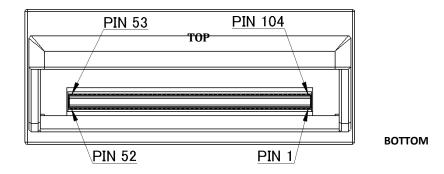

# **Electrical Pad Layout**

**Pin Descriptions**

| Pin | Symbol    | I/O | Description                   | Logic               | Pin | Symbol  | I/O | Description                    | Logic |

|-----|-----------|-----|-------------------------------|---------------------|-----|---------|-----|--------------------------------|-------|

| 1   | GND       |     | Ground                        |                     | 53  | GND     |     | Ground                         |       |

| 2   | OHIO_RDn  | 0   | Overhead extraction           |                     | 54  | RX7p    | 0   | Ch7 25Gbps Receive Output      | CML   |

| 3   | OHIO_RDp  | _   |                               |                     | 55  | RX7n    |     |                                |       |

| 4   | GND       |     | Ground                        |                     | 56  | GND     |     | Ground                         |       |

| 5   | OHIO_TDn  | ı   | Overhead insertion            |                     | 57  | RX0p    | 0   | Ch0 25Gbps Receive Output      | CML   |

| 6   | OHIO_TDp  |     |                               |                     | 58  | RX0n    |     |                                |       |

| 7   | 3.3V_GND  |     | Ground                        |                     | 59  | GND     |     | Ground                         |       |

| 8   | 3.3V_GND  |     |                               |                     | 60  | RX1p    | 0   | Ch1 25Gbps Receive Output      | CML   |

| 9   | 3.3V      |     | 2.27/ Danier Consults         |                     | 61  | RX1n    |     |                                |       |

| 10  | 3.3V      |     | 3.3V Power Supply             |                     | 62  | GND     |     | Ground                         |       |

| 11  | 3.3V      |     |                               |                     | 63  | RX6p    | 0   | Ch6 25Gbps Receive Output      | CML   |

| 12  | 3.3V      |     |                               |                     | 64  | RX6n    |     |                                |       |

| 13  | 3.3V_GND  |     | Ground                        |                     | 65  | GND     |     | Ground                         |       |

| 14  | 3.3V_GND  |     |                               |                     | 66  | RX5p    | 0   | Ch5 25Gbps Receive Output      | CML   |

| 15  | VND_IO_A  |     | Do not connect                |                     | 67  | RX5n    |     |                                |       |

| 16  | VND_IO_B  |     |                               |                     | 68  | GND     |     | Ground                         |       |

| 17  | PRG_CNTL1 |     | Programmable Control 1        | LVCMOS<br>w/ PUR    | 69  | RX2p    | 0   | Ch2 25Gbps Receive Output      | CML   |

| 18  | PRG_CNTL2 |     | Programmable Control 2        | W/ FOR              | 70  | RX2n    |     |                                |       |

| 19  | PRG_CNTL3 |     | Programmable Control 3        |                     | 71  | GND     |     | Ground                         |       |

| 20  | PRG_ALRM1 |     | Programmable Alarm 1          | LVCN4OC             | 72  | RX3p    | 0   | Ch3 25Gbps Receive Output      | CML   |

| 21  | PRG_ALRM2 | 0   | Programmable Alarm 2          | LVCMOS              | 73  | RX3n    |     |                                |       |

| 22  | PRG_ALRM3 |     | Programmable Alarm 3          |                     | 74  | GND     |     | Ground                         |       |

| 23  | GND       |     | Ground                        |                     | 75  | RX4p    |     | Ch 4 35 Chara Basadias Outroot | CNAL  |

| 24  | TX_DIS    | ı   | Transmitter Disable           | LVCMOS w/ PUR       | 76  | RX4n    | 0   | Ch4 25Gbps Receive Output      | CML   |

| 25  | RX_LOS    | 0   | Loss of Optical Input Signal  | LVCMOS              | 77  | GND     |     | Ground                         |       |

| 26  | MOD_LOPWR | I   | Module Low Power Mode         | LVCMOS w/ PUR       | 78  | REFCLKp |     | Not Head                       |       |

| 27  | MOD_ABS   | 0   | Module Absent Indicator       | GND                 | 79  | REFCLKn |     | Not Used                       |       |

| 28  | MOD_RSTn  | I   | Module Reset                  | LVCMOS w/ PDR       | 80  | GND     |     | Ground                         |       |

| 29  | GLB_ALRMn | 0   | Global Alarm                  | LVCMOS (open drain) | 81  | TX7p    | I   | Ch7 25Gbps Transmit Input      | CML   |

| 30  | GND       |     | Ground                        |                     | 82  | TX7n    |     |                                |       |

| 31  | MDC       | 1   | Management Data Clock         | 1.2V CMOS           | 83  | GND     |     | Ground                         |       |

| 32  | MDIO      | I/O | Management bi-dir. Data       | 1.2V CMOS           | 84  | ТХОр    |     | Ch0 25Gbps Transmit Input      | CML   |

| 33  | PRTADR0   | - 1 | MDIO Physical Port addr. bit0 | 1.2V CMOS           | 85  | TX0n    | Ľ   | Cho 250bps Transmit input      | CIVIL |

| 34  | PRTADR1   |     | MDIO Physical Port addr. bit1 |                     | 86  | GND     |     | Ground                         |       |

| 35  | PRTADR2   |     | MDIO Physical Port addr. bit2 |                     | 87  | TX1p    | I   | Ch1 25Gbps Transmit Input      | CML   |

| 36 | VND_IO_C     |   |                              | 88  | TX1n |   |                           |     |

|----|--------------|---|------------------------------|-----|------|---|---------------------------|-----|

| 37 | VND_IO_D     |   | Do not connect               | 89  | GND  |   | Ground                    |     |

| 38 | VND_IO_E     |   |                              | 90  | ТХ6р | I | Ch6 25Gbps Transmit Input | CML |

| 39 | 3.3V_GND     |   | Ground                       | 91  | TX6n |   |                           |     |

| 40 | 3.3V_GND     |   | Ground                       | 92  | GND  |   | Ground                    |     |

| 41 | 3.3V         |   |                              | 93  | TX5p | I | Ch5 25Gbps Transmit Input | CML |

| 42 | 3.3V         |   | 3.3V Power Supply            | 94  | TX5n |   |                           |     |

| 43 | 3.3V         |   |                              | 95  | GND  |   | Ground                    |     |

| 44 | 3.3V         |   |                              | 96  | TX2p | ı | Ch2 25Gbps Transmit Input | CML |

| 45 | 3.3V_GND     |   | Ground                       | 97  | TX2n |   |                           |     |

| 46 | 3.3V_GND     |   |                              | 98  | GND  |   | Ground                    |     |

| 47 | OHIO_REFCLKn | 1 | Overhead I/O Reference Clock | 99  | TX3p | ı | Ch3 25Gbps Transmit Input | CML |

| 48 | OHIO_REFCLKp |   |                              | 100 | TX3n |   |                           |     |

| 49 | GND          |   | Ground                       | 101 | GND  |   | Ground                    |     |

| 50 | RX_MCLKn     |   | Not for normal use           | 102 | TX4p | I | Ch4 25Gbps Transmit Input | CML |

| 51 | RX_MCLKp     |   |                              | 103 | TX4n |   |                           |     |

| 52 | GND          |   | Ground                       | 104 | GND  |   | Ground                    |     |

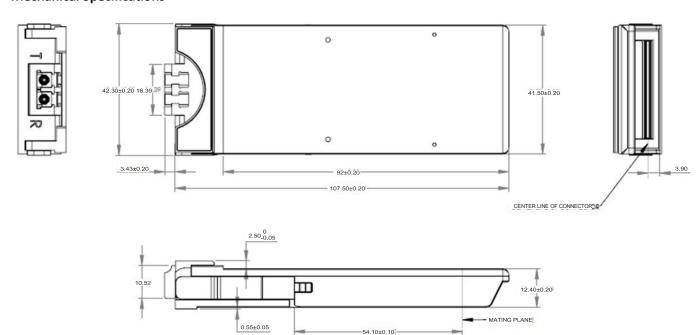

# **Mechanical Specifications**

## **OptioConnect**

## Innovation for the Future of High-Speed Networking

#### Who We Are

OptioConnect is reshaping the landscape of communication and high-speed networking through intelligent technology. With a core focus on cutting edge technology, we deliver smarter fiber optic solutions for enterprise networks, data centers, and next-gen telecom infrastructures.

### What We Do

At OptioConnect, we fuse advanced engineering with intelligent automation to drive the future of networking. Our Al-integrated solutions are designed to optimize performance and streamline operations with:

- Superior Performance

- Network and traffic optimization

- Intelligent energy management

- Seamless OEM compatibility

- Scalable cost-efficiency

## **Smarter Networks by Design**

Innovation isn't just a goal—it's our process. We embed AI and machine learning across our R&D and product lines, enabling adaptive performance, automated tuning, and faster deployment cycles. The result? Networks that don't just work—they learn, evolve, and outperform.

## **Our Team**

Our engineers, data scientists, and network architects bring decades of experience and a future-focused mindset. We provide hands-on support with intelligent insights that turn complex challenges into simple solutions.

## **Our Mission**

To deliver AI-enhanced connectivity that reduces cost, increases speed, and maximizes efficiency—empowering our partners to operate at the forefront of a rapidly evolving digital world.

## **Let's Connect**

Discover how OptioConnect's intelligent infrastructure solutions can power your network's next leap forward. <a href="https://www.optioconnect.com">www.optioconnect.com</a> | info@optioconnect.com