# **addon**

#### 10GBASE-LR-AO

Enterasys® 10GBASE-LR Compatible TAA 10GBase-LR XENPAK Transceiver (SMF, 1310nm, 10km, SC, DOM)

#### **Features**

- INF-8474 Compliance

- Duplex SC Connector

- Commercial Temperature 0 to 70 Celsius

- Single-mode Fiber

- Hot Pluggable

- Excellent ESD Protection

- Metal with Lower EMI

- RoHS Compliant and Lead Free

### **Applications**

- 8x/10x Fibre Channel

- 10GBase-LR Ethernet

- Access, Datacenter and Enterprise

- Mobile Fronthaul CPRI/OBSAI

#### **Product Description**

This Enterasys® 10GBASE-LR compatible XENPAK transceiver provides 10GBase-LR throughput up to 10km over single-mode fiber (SMF) using a wavelength of 1310nm via an SC connector. It can operate at temperatures between 0 and 70C. Our transceiver is built to meet or exceed OEM specifications and is guaranteed to be 100% compatible with Enterasys®. It has been programmed, uniquely serialized, and tested for data-traffic and application to ensure that it will initialize and perform identically. All of our transceivers comply with Multi-Source Agreement (MSA) standards to provide seamless network integration. Additional product features include Digital Optical Monitoring (DOM) support which allows access to real-time operating parameters. This transceiver is Trade Agreements Act (TAA) compliant. We stand behind the quality of our products and proudly offer a limited lifetime warranty.

AddOn's transceivers are RoHS compliant and lead-free.

TAA refers to the Trade Agreements Act (19 U.S.C. & 2501-2581), which is intended to foster fair and open international trade. TAA requires that the U.S. Government may acquire only "U.S.-made or designated country end products.")

## **Absolute Maximum Ratings**

| Parameter                         |                            | Symbol | Min.  | Тур.    | Max.   | Unit | Notes |

|-----------------------------------|----------------------------|--------|-------|---------|--------|------|-------|

| Storage Ambient Temperature Range |                            | Tstg   | -40   |         | +85    | °C   |       |

| Powered Case Ten                  | nperature Range            |        |       |         | +70    | °C   |       |

| Supply Voltage AP                 | S                          | Vaps   |       |         | 1.5    | V    |       |

| Supply Voltage Ra                 | nge @ 3.3V                 | Vcc3   | -0.5  |         | 4.0    | V    |       |

| Operating Case Te                 | Operating Case Temperature |        |       |         | +70    | °C   |       |

| Power Supply Volt                 | Power Supply Voltage       |        | 3.13  | 3.3     | 3.47   | V    |       |

|                                   |                            |        | 1.152 | 1.2     | 1.248  |      |       |

| Power Dissipation                 |                            | PD     |       | 3.5     | 4      | W    |       |

| Operating Range                   | Single-Mode Fiber          | Lop    | 2     |         | 10,000 | m    |       |

| Data Rate                         | 10GBASE-LR<br>Module       | DR     |       | 10.3125 |        | Gbps |       |

## **Electrical DC Characteristics**

| Parameter                                                                           | Symbol     | Min. | Тур. | Max. | Unit | Notes |  |  |

|-------------------------------------------------------------------------------------|------------|------|------|------|------|-------|--|--|

| 1.2V CMOS (1.8V CMOS Compatible) I/O DC Characteristics (PRTAD;LASI;RESET;TX_ONOFF) |            |      |      |      |      |       |  |  |

| Output High Voltage                                                                 | VOH        | 1    |      |      | V    | 1     |  |  |

| Output Low Voltage                                                                  | VOL        |      |      | 0.15 | V    |       |  |  |

| Input High Voltage                                                                  | VIH        | 0.84 |      | 1.5  | V    |       |  |  |

| Input Low Voltage                                                                   | VIL        |      |      | 0.36 | V    |       |  |  |

| Input Pull-Down Current                                                             | IPD        | 20   |      | 120  | uA   |       |  |  |

| XAUI I/O DC Characteristics (TXLANE[03]; R.                                         | XLANE[03]) |      |      |      |      |       |  |  |

| Differential Input Amplitude (Pk-Pk)                                                |            | 220  |      | 1600 | mV   | 4     |  |  |

| Differential Output Amplitude (Pk-Pk)                                               |            | 800  |      | 1600 |      | 4     |  |  |

| MDIO I/O DC Characteristics (MDIO; MDC)                                             |            |      |      |      |      |       |  |  |

| Output Low Voltage                                                                  | VOL        | -0.3 |      | 0.2  | V    |       |  |  |

| Output Low Current                                                                  | IOL        |      |      | 20   | mA   |       |  |  |

| Input High Voltage                                                                  | VIH        | 0.84 |      | 1.5  | V    |       |  |  |

| Input Low Voltage                                                                   | VIL        | -0.3 |      | 0.36 | V    |       |  |  |

## Notes:

- 1. For 1.8V CMOS, VOH=1.65V (minimum), VOL=0.15V (maximum), VIH=1.17V (minimum), and VIL = 0.63V (maximum).

- 2. Rpull-up= $10k\Omega$  to 1.86V.

- 3. VIN=1.8V.

- 4. AC coupled.

## **Electrical AC Characteristics**

| Parameter                                         | Symbol | Min.          | Тур.           | Max.           | Unit | Notes |

|---------------------------------------------------|--------|---------------|----------------|----------------|------|-------|

| XAUI Input AC Characteristics (TXLANE[03])        |        |               |                |                |      |       |

| XAUI Baud Rate                                    | DRin   |               | 3.125          |                | Gbps |       |

| Differential Input Impedance                      | ZIN    | 80            | 100            | 120            | Ω    |       |

| XAUI Output AC Characteristics (RXLANE[03])       |        |               |                |                |      |       |

| XAUI Baud Rate                                    | DRout  |               | 3.125          |                | Gbps |       |

| XAUI Eye Mask (Far-End)                           |        | Accord        | ing to IEEE 80 | )2.3ae         |      | 3     |

| Output Differential Impedance                     | ZO     | 80            | 100            | 120            | Ω    |       |

| Total Jitter                                      | TJXAUI |               |                | 0.35           | UI   | 4     |

| Deterministic Jitter                              | DJXAUI |               |                | 0.37           | UI   | 4     |

| Power-On Reset AC Characteristics                 |        |               |                |                |      |       |

| Power-On Reset AC Characteristics                 | Acco   | rding to XENI | PAK MSA Issu   | ie 3.0, 2002-9 | 9-18 |       |

| MDIO I/O AC Characteristics (MDIO; MDC)           |        |               |                |                |      |       |

| MDIO Data Hold Time                               | tHOLD  | 10            |                |                | ns   |       |

| MDIO Data Set-Up Time                             | tSU    | 10            |                |                | ns   |       |

| Delay from MDC Rising Edge to MDIO Data<br>Change | tDELAY |               |                | 300            | ns   | 2     |

| MDC Clock Rate                                    | fMAX   |               |                | 2.5            | MHz  | 1     |

## Notes:

- 1. 100MHz to 2.5GHz.

- 2. At crossing point.

- 3. Per IEEE Std 802.3ae.

- 4. At near-end, no pre-equalization, 1UI = 320ps.

## **Optical Characteristics**

| Parameter                               | Symbol | Min.    | Тур.          | Max.  | Unit  | Notes |

|-----------------------------------------|--------|---------|---------------|-------|-------|-------|

| Transmitter                             |        |         |               |       |       |       |

| Average Launch Power                    | Pavg   | -8.2    |               | -0.5  | dBm   |       |

| Transmitter and Dispersion Penalty      | TDP    |         |               | 3.2   | dB    |       |

| Center Wavelength Range                 | λ      | 1260    | 1310          | 1355  | nm    |       |

| Side-Mode Suppression Ratio             | SMSR   | 30      |               |       | dB    |       |

| Extinction Ratio                        | ER     | 4.0     | 6             |       | dB    |       |

| RIN <sub>12</sub> OMA                   | RIN    |         |               | -128  | dB/Hz |       |

| Eye Mask Definition                     |        | Accordi | ng to IEEE 80 | 2.3ae |       | 1     |

| Optical Return Loss Tolerance           | ORLT   |         |               | 12    | dB    |       |

| Average Launch Power of Off Transmitter | Poff   |         |               | -30   | dBm   |       |

| Receiver                                |        |         |               |       |       |       |

| Stressed Receiver Sensitivity in OMA    | Psen   |         |               | -10.3 | dBm   | 2     |

| Receiver Sensitivity in OMA             | Psen   |         |               | -12.6 | dBm   | 2     |

| Power Overload                          | Ро     | 0.5     |               |       | dBm   |       |

| Signal Detect Assert Level              | PSD    |         |               | -13   | dBm   |       |

| Signal Detect Hysteresis                | PSD    | 1       |               |       | dB    |       |

| Center Wavelength Range                 | λ      | 1260    |               | 1355  | nm    |       |

## Notes:

- 1. Conforms to IEEE triple trade-off between center wavelength, RMS spectral width, and minimum OMA.

- 2. Receiver sensitivity, which is defined for an ideal input signal, is informative only.

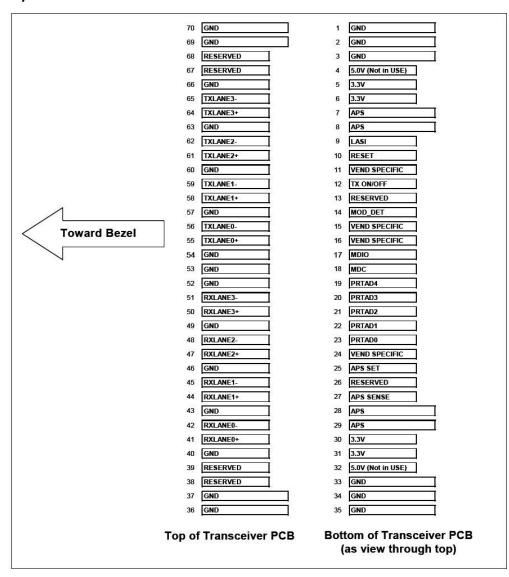

# **Pin Descriptions**

| Item # | Signal Name                        | Level      | I/O | Pin                                                                                   | Name/Description                                                                                                                                                      |

|--------|------------------------------------|------------|-----|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | GND                                |            |     | 1, 2, 3, 33, 34, 35, 36, 37,<br>40, 43, 46, 49, 52, 53, 54,<br>57, 60, 63, 66, 69, 70 | Ground connection for signal ground on the module.                                                                                                                    |

| 2      | APS                                | +1.2V      |     | 7, 8, 28, 29                                                                          | Input from Adaptive Power Supply.                                                                                                                                     |

| 3      | APS SENSE                          | +1.2V      |     | 27                                                                                    | APS Sense Output. Connected to the APS sense output. Connected to the APS input from APS.                                                                             |

| 4      | APS SET                            |            |     | 25                                                                                    | Feedback Input from APS. Connected to the GND through a $1.18 \mathrm{k}\Omega$ resistor inside the transponder.                                                      |

| 5      | 3.3V                               | +3.3 V DC  |     | 5, 6, 30, 31                                                                          | DC Power Input,+5.0V DC, Nominal.                                                                                                                                     |

| 6      | Reserved                           |            |     | 25                                                                                    | Reserved for APD.                                                                                                                                                     |

| 7      | Reserved                           |            |     | 13                                                                                    | Reserved.                                                                                                                                                             |

| 8      | MDIO                               | Open Drain | I/O | 17                                                                                    | Management Data I/O. Requires external $10\text{-}22\text{k}\Omega$ pull-up to the APS on the host.                                                                   |

| 9      | MDC                                | 1.2V CMOS  | 1   | 18                                                                                    | Management Data Clock Input.                                                                                                                                          |

| 10     | PRTAD4                             | 1.2V CMOS  | 1   | 19                                                                                    | Port Address Input Bit 4.                                                                                                                                             |

| 11     | PRTAD3                             | 1.2V CMOS  | 1   | 20                                                                                    | Port Address Input Bit 3.                                                                                                                                             |

| 12     | PRTAD2                             | 1.2V CMOS  | 1   | 21                                                                                    | Port Address Input Bit 2.                                                                                                                                             |

| 13     | PRTAD1                             | 1.2V CMOS  | 1   | 22                                                                                    | Port Address Input Bit 1.                                                                                                                                             |

| 14     | PRTAD0                             | 1.2V CMOS  | 1   | 23                                                                                    | Port Address Input Bit 0.                                                                                                                                             |

| 15     | LASI                               | Open Drain | 0   | 9                                                                                     | Link Alarm Status Interrupt Output. Open drain compatible output with 10 - 20kΩ pullup on the host. Logic high = normal operation. Logic low = status flag triggered. |

| 16     | RESET                              | Open Drain | I   | 10                                                                                    | Reset Input. Open drain compatible input with $22k\Omega$ pull-up to APS internal to the transponder. Logic high = normal operation. Logic low = reset.               |

| 17     | Vendor-Specific                    |            |     | 11, 15, 16, 24                                                                        | Vendor-Specific Pins. Leave unconnected when not used.                                                                                                                |

| 18     | TX ON/OFF                          | Open Drain | I   | 12                                                                                    | TX ON/OFF Input. Open drain compatible input with $22k\Omega$ pull-up to APS internal to the transponder. Logic high = transmitter on. Logic low = transmitter off.   |

| 19     | MOD DETECT                         |            | 0   | 14                                                                                    | Pulled low inside the transponder through a $1k\Omega$ resistor to the ground.                                                                                        |

| 20     | Reserved                           |            | _   | 67, 68, 38, 39                                                                        | Reserved for future use.                                                                                                                                              |

| 21     | TX LANE 3-<br>TX LANE 3+           |            | 1   | 65<br>64                                                                              | Module XAUI Input Lane 3– Module XAUI Input Lane 3+                                                                                                                   |

| 22     | TX LANE 2-<br>TX LANE 2+           |            | ı   | 62<br>61                                                                              | Module XAUI Input Lane 2– Module XAUI Input Lane 2+                                                                                                                   |

| 23     | TX LANE 2+  TX LANE 1-  TX LANE 1+ |            | 1   | 59<br>58                                                                              | Module XAUI Input Lane 2+  Module XAUI Input Lane 1-  Module XAUI Input Lane 1+                                                                                       |

| 24 | TX LANE 0- | 1 | 56 | Module XAUI Input Lane 0–  |

|----|------------|---|----|----------------------------|

| 24 | TX LANE 0+ | 1 | 55 | Module XAUI Input Lane 0+  |

| 25 | RX LANE 0+ | 0 | 41 | Module XAUI Output Lane 0+ |

| 25 | RX LANE 0- | U | 42 | Module XAUI Output Lane 0– |

| 26 | RX LANE 1+ | 0 | 44 | Module XAUI Output Lane 1+ |

| 20 | RX LANE 1- | U | 45 | Module XAUI Output Lane 1– |

| 27 | RX LANE 2+ | 0 | 47 | Module XAUI Output Lane 2+ |

| 21 | RX LANE 2- | U | 48 | Module XAUI Output Lane 2– |

| 20 | RX LANE 3+ | 0 | 50 | Module XAUI Output Lane 3+ |

| 28 | RX LANE 3- | 0 | 51 | Module XAUI Output Lane 3– |

## **Electrical Pad Layout**

# **Host PCB Xenpak Pin-Out**

| 1  | GND               | GND      | 70 |

|----|-------------------|----------|----|

| 2  | GND               | GND      | 69 |

| 3  | GND               | RESERVED | 68 |

| 4  | 5.0V (Not in USE) | RESERVED | 67 |

| 5  | 3.3V              | GND      | 66 |

| 6  | 3.3V              | TXLANE3- | 65 |

| 7  | APS               | TXLANE3+ | 64 |

| 8  | APS               | GND      | 63 |

| 9  | LASI              | TXLANE2- | 62 |

| 10 | RESET             | TXLANE2+ | 61 |

| 11 | VEND SPECIFIC     | GND      | 60 |

| 12 | TX ON/OFF         | TXLANE1- | 59 |

| 13 | RESERVED          | TXLANE1+ | 58 |

| 14 | MOD_DET           | GND      | 57 |

| 15 | VEND SPECIFIC     | TXLANE0- | 56 |

| 16 | VEND SPECIFIC     | TXLANE0+ | 55 |

| 17 | MDIO              | GND      | 54 |

| 18 | MDC               | GND      | 53 |

| 19 | PRTAD4            | GND      | 52 |

| 20 | PRTAD3            | RXLANE3- | 51 |

| 21 | PRTAD2            | RXLANE3+ | 50 |

| 22 | PRTAD1            | GND      | 49 |

| 23 | PRTAD0            | RXLANE2- | 48 |

| 24 | VEND SPECIFIC     | RXLANE2+ | 47 |

| 25 | APS SET           | GND      | 46 |

| 26 | RESERVED          | RXLANE1- | 45 |

| 27 | APS SENSE         | RXLANE1+ | 44 |

| 28 | APS               | GND      | 43 |

| 29 | APS               | RXLANE0- | 42 |

| 30 | 3.3V              | RXLANE0+ | 41 |

| 31 | 3.3V              | GND      | 40 |

| 32 | 5.0V (Not in USE) | RESERVED | 39 |

| 33 | GND               | RESERVED | 38 |

| 34 | GND               | GND      | 37 |

| 35 | GND               | GND      | 36 |

|    |                   |          |    |

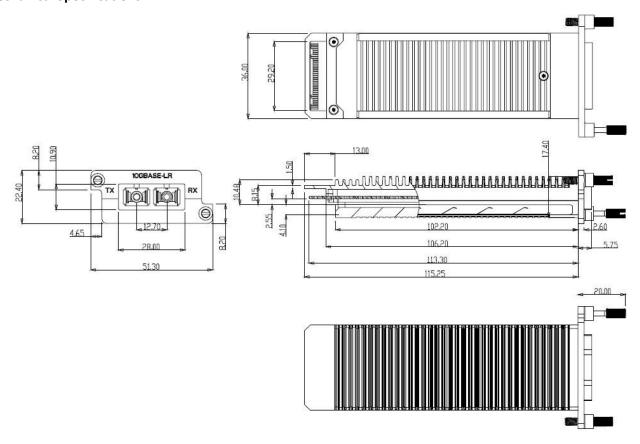

# **Mechanical Specifications**

#### **About AddOn Networks**

In 1999, AddOn Networks entered the market with a single product. Our founders fulfilled a severe shortage for compatible, cost-effective optical transceivers that compete at the same performance levels as leading OEM manufacturers. Adhering to the idea of redefining service and product quality not previously had in the fiber optic networking industry, AddOn invested resources in solution design, production, fulfillment, and global support.

Combining one of the most extensive and stringent testing processes in the industry, an exceptional free tech support center, and a consistent roll-out of innovative technologies, AddOn has continually set industry standards of quality and reliability throughout its history.

Reliability is the cornerstone of any optical fiber network and is in engrained in AddOn's DNA. It has played a key role in nurturing the long-term relationships developed over the years with customers. AddOn remains committed to exceeding industry standards with certifications from ranging from NEBS Level 3 to ISO 9001:2005 with every new development while maintaining the signature reliability of its products.

## **U.S. Headquarters**

Email: sales@addonnetworks.com

Telephone: +1 877.292.1701

Fax: 949.266.9273

#### **Europe Headquarters**

Email: salessupportemea@addonnetworks.com

Telephone: +44 1285 842070