# •addon

## 57-1000328-01-AO

Brocade<sup>®</sup> (Formerly) 57-1000328-01 Compatible TAA 100GBase-ER4 CFP2 Transceiver (SMF, 1310nm, 40km, LC, DOM)

## Features

- CFP MSA 1.0 Compliance

- Duplex LC Connector

- Commercial Temperature 0 to 70 Celsius

- Single-mode Fiber

- Hot Pluggable

- Excellent ESD Protection

- Metal with Lower EMI

- RoHS Compliant and Lead Free

#### **Applications**

- 100GBase Ethernet

- Access and Enterprise

## **Product Description**

This Brocade<sup>®</sup> (Formerly) 57-1000328-01 compatible CFP2 transceiver provides 100GBase-ER4 throughput up to 40km over single-mode fiber (SMF) using a wavelength of 1310nm via an LC connector. It is guaranteed to be 100% compatible with the equivalent Brocade<sup>®</sup> (Formerly) transceiver. This easy to install, hot swappable transceiver has been programmed, uniquely serialized and data-traffic and application tested to ensure that it will initialize and perform identically. Digital optical monitoring (DOM) support is also present to allow access to real-time operating parameters. This transceiver is Trade Agreements Act (TAA) compliant. We stand behind the quality of our products and proudly offer a limited lifetime warranty.

AddOn's transceivers are RoHS compliant and lead-free.

TAA refers to the Trade Agreements Act (19 U.S.C. & 2501-2581), which is intended to foster fair and open international trade. TAA requires that the U.S. Government may acquire only "U.S. – made or designated country end products."

## **Absolute Maximum Ratings**

| Parameter                   | Symbol | Min. | Max. | Unit |

|-----------------------------|--------|------|------|------|

| Storage Temperature         | Ts     | -40  | 85   | °C   |

| Supply Voltage              | Vcc    | -0.5 | 3.6  | V    |

| Operating Relative Humidity | RH     | 0    | 85   | %    |

Note:

1. Exceeding any one of these values may destroy the device immediately.

# **Recommended Operating Conditions**

| Parameter                  | Symbol | Min. | Тур.  | Max. | Unit |

|----------------------------|--------|------|-------|------|------|

| Operating Case Temperature | ТС     | 0    |       | 70   | °C   |

| Power Supply Voltage       | Vcc    | 3.14 | 3.3   | 3.46 | V    |

| Data Rate                  | DR     |      | 103.2 | 112  | Gb/s |

## **Electrical Characteristics**

| Parameter                       |                     |              | Symbol                | Min.               | Тур.    | Max. | Unit    | Notes |

|---------------------------------|---------------------|--------------|-----------------------|--------------------|---------|------|---------|-------|

| Voltage Supply Electr           | ical Char           | racteristics |                       |                    |         |      |         |       |

| Supply Current                  | Tx Se               | ction        | lcc                   | A                  |         |      | 3.75    | 1     |

|                                 | Rx Se               | ction        |                       |                    |         |      |         |       |

| Power Supply Noise              |                     |              | Vrip                  |                    |         |      | 2% DC   | 1MHz  |

|                                 |                     |              |                       |                    |         |      | 3% 1    | 10MHz |

| Total Dissipation               | Class               | 1            |                       |                    |         |      | 3       |       |

| Power                           | Class               |              | Pw                    | w                  |         |      | 6       | _     |

|                                 | Class               | -            |                       |                    |         |      | 9       | _     |

|                                 | Class               |              |                       |                    |         |      | 12      |       |

| Low Power Mode Dis              | -                   |              | Plow                  | W                  |         |      | 2       |       |

| Inrush Current                  | Class1              | and          | I-inrush              | mA/usec            | 100     |      | 100     |       |

| Turn-off Current Inrush Current | Class2<br>Class3    | and          | I-turnoff<br>I-inrush | mA/usec<br>mA/usec | -100    |      | 200     |       |

| Turn-off Current                | Class5              | anu          | I-turnoff             | mA/usec            | -200    |      | 200     |       |

| Different Signal Elect          |                     | racteristics | 1 turnon              | mAy usee           | 200     |      |         |       |

| Single Ended Data Ing           |                     |              |                       | mV                 | 20      |      | 525     |       |

|                                 |                     |              |                       |                    |         |      |         |       |

| Single Ended Data Ou            |                     | -            |                       | mV                 | 180     |      | 385     |       |

| Differential Signal Ou          | -                   |              |                       | Ω                  | 80      |      | 120     |       |

| Differential Signal Inp         |                     |              |                       | Ω                  | 80      |      | 120     |       |

| 3.3V LVCMOS Electric            | cal Chara           | cteristics   |                       |                    |         |      |         |       |

| Input High Voltage              |                     |              | 3.3VIH                | V                  | 2.0     |      | Vcc+0.3 |       |

| Input Low Voltage               |                     |              | 3.3VIL                | V                  | -0.3    |      | 0.8     |       |

| Input Leakage Curren            | t                   |              | 3.3IIN                | uA                 | -10     |      | +10     |       |

| Output High Voltage             | (IOH=10             | 0uA)         | 3.3VOH                | V                  | Vcc-0.2 |      |         |       |

| Output Low Voltage              | (IOL=100            | uA)          | 3.3VOL                | V                  |         |      | 0.2     |       |

| Minimum Pulse Widt<br>Signal    | h of Con            | trol Pin     | t_CNTL                | us                 | 100     |      |         |       |

| 1.2V LVCMOS Electric            | cal Chara           | cteristics   |                       |                    |         |      |         |       |

| Input High Voltage              |                     |              | 1.2VIH                | V                  | 0.84    |      | 1.5     |       |

| Input Low Voltage               |                     | 1.2VIL V     | 0.3                   | 1.2VIL V           |         | 0.36 |         |       |

| Input Leakage Current           |                     | 1.2IIN       | uA                    | -100               |         | +100 |         |       |

| Output High Voltage             | Output High Voltage |              | 1.2VOH                | V                  | 1.0     |      | 1.5     |       |

| Output Low Voltage              |                     |              | 1.2VOL                | V                  | -0.3    |      | 0.2     |       |

| Output High Current             |                     |              | 1.2IOH                | mA                 |         |      | -4      |       |

| Output Low Current              |                     |              | 1.2IOL                | mA                 | +4      |      |         |       |

| Input Capacitance               |                     |              | Ci                    | pF                 |         |      | 10      |       |

# **High Speed Electrical Characteristics**

| Parameter               | Symbol | Unit | Min.        | Max. | Notes                                                                     |  |                              |

|-------------------------|--------|------|-------------|------|---------------------------------------------------------------------------|--|------------------------------|

| Impedance               | Zd     | Ω    | 90          | 110  |                                                                           |  |                              |

| Frequency               |        | MHz  | 161.1328125 |      | 161.1328125                                                               |  | 1/64 of electrical lane rate |

| Frequency Stability     | ∆f     | ppm  | -100        | 100  | For Ethernet                                                              |  |                              |

|                         |        |      | -20         | 20   | For Telecom                                                               |  |                              |

| Differential Voltage    | VDIFF  | mV   | 400         | 900  | Peak to Peak Differential                                                 |  |                              |

| Common mode noise (rms) |        | mV   |             | 17.5 |                                                                           |  |                              |

| RMS jitter              |        | ps   |             | 10   | Random Jitter Over frequency<br>band of 10KHZ <f<10mhz< th=""></f<10mhz<> |  |                              |

| Clock Duty Cycle        |        | %    | 40          | 60   |                                                                           |  |                              |

# **Optical Characteristics**

| Parameter                                                 | Symbol | Min.          | Тур.             | Max.    | Unit | Notes   |

|-----------------------------------------------------------|--------|---------------|------------------|---------|------|---------|

| Transmitter                                               |        |               |                  |         |      |         |

| Signaling Rate per Lane                                   |        | 25.78125 ±    | 100 ppm          |         | GBd  | 9       |

|                                                           |        | 27.9525 ±2    | 0 ppm            |         | GBd  | OTU4    |

| Four Lane Wavelength Range                                | λ1     | 1294.53       | 1295.56          | 1296.59 | nm   |         |

|                                                           | λ2     | 1299.02       | 1300.05          | 1301.09 | nm   |         |

|                                                           | λ3     | 1303.54       | 1304.58          | 1305.63 | nm   |         |

|                                                           | λ4     | 1308.09       | 1309.14          | 1310.19 | nm   |         |

| Total launch power                                        |        |               |                  | 8.9     | dBm  | 9       |

| Average launch power, each lane                           | Pavg   | -2.9          |                  | 2.9     | dBm  | 2       |

| Optical modulation amplitude, each lane<br>(OMA)2         | OMA    | 0.1           |                  | 4.5     | dBm  |         |

| Difference in launch power between any two<br>lanes (OMA) |        |               |                  | 3.6     | dB   |         |

| Extinction ratio                                          | ER     | 8             |                  |         | dB   | 9       |

| Side-mode suppression ratio                               | SMSR   | 30            |                  |         | dB   |         |

| Transmitter and dispersion penalty, each lane             | TDP    |               |                  | 2.5     | dB   |         |

| Optical return loss tolerance                             |        |               |                  | 20      | dB   |         |

| Transmitter reflectance3                                  |        |               |                  | -12     | dB   |         |

| Transmitter eye mask {X1, X2, X3, Y1, Y2, Y3}             |        | {0.25, 0.4, 0 | 0.45, 0.25, 0.28 | 3, 0.4} |      | 9       |

| Receiver                                                  |        |               | _                |         |      |         |

| Receive Rate for Each Lane                                |        |               | 25.78125         | 27.9525 | Gbps |         |

| Overload Input Optical Power                              | Pmax   | 5.5           |                  |         | dBm  | 3       |

| Average Receive Power for Each Lane                       | Pin    | -16           |                  | 4.5     | dBm  | 4, 5 (- |

|                                                             |        |  |     |     | 20.9)           |

|-------------------------------------------------------------|--------|--|-----|-----|-----------------|

| Receive Power in OMA for Each Lane                          | PinOMA |  | 4.5 | dBm |                 |

| Difference in Receive Power in OMA between<br>Any Two Lanes |        |  | 4.5 | dBm |                 |

| Receiver Sensitivity in OMA for Each Lane                   | SOMA   |  | -16 | dBm | 6 (-21.4)       |

| Stressed Receiver Sensitivity in OMA for Each<br>Lane       |        |  | -12 | dBm | 7,8 (-<br>17.9) |

## Notes:

- 1. The supply current includes CFP2 module's supply current and test board working current.

- 2. Average launch power, each lane (min) is informative for 100GBase-LR4, not the principal indicator of signal strength.

- 3. The receiver shall be able to tolerate, without damage, continuous exposure to an optical input signal having this average power level

- 4. The average receive power, each lane (max) for 100GBASE-ER4 is larger than the 100BASE-ER4 transmitter value to allow compatibility with 100BASE-LR4 units at short distances

- Average receive power, each lane (min) is informative and not the principal indicator of signal strength. A received power below this value cannot be compliant; however, a value above this does not ensure compliance

- 6. Receiver sensitivity (OMA), each lane (max) is informative

- 7. Measured with conformance test signal at TP3 for BER=10-12

- 8. Conditions of stressed receiver sensitivity test: vertical eye closure penalty for each lane is 1.8dB; stressed eye J2 jitter for each lane is 0.3UI; stressed eye J9 jitter for each lane is 0.47UI.

- 9. 100GBase-ER4

## **Pin Descriptions**

| Pin | Name       | I/O | Logic            | Description                                                                                                                                   |

|-----|------------|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND        |     |                  |                                                                                                                                               |

| 2   | (TX_MCLKn) | 0   | CML              | For optical waveform testing. Not for normal use.                                                                                             |

| 3   | (TX_MCLKp) | 0   | CML              | For optical waveform testing. Not for normal use.                                                                                             |

| 4   | GND        |     |                  |                                                                                                                                               |

| 5   | N.C        |     |                  | No Connect                                                                                                                                    |

| 6   | N.C        |     |                  | 3.3V ± 5%                                                                                                                                     |

| 7   | 3.3V_GND   |     |                  | 3.3V Module Supply Voltage Return Ground, can be separate or tied together with Signal Ground                                                 |

| 8   | 3.3V_GND   |     |                  | 3.3V Module Supply Ground, internally connected to Signal Ground                                                                              |

| 9   | 3.3V       |     |                  | 3.3V Module Supply Voltage                                                                                                                    |

| 10  | 3.3V       |     |                  | Module Vendor I/O B, NC                                                                                                                       |

| 11  | 3.3V       |     |                  | "1" or NC = transmitter disabled,<br>"0" = transmitter enabled                                                                                |

| 12  | 3.3V       |     |                  | "1" = loss of signal (low optical signal), "0" = normal condition                                                                             |

| 13  | 3.3V_GND   |     |                  | 3.3V Module Supply Voltage Return Ground, can be separate or tied together with Signal Ground                                                 |

| 14  | 3.3V_GND   |     |                  | "1" or NC = module in low power (safe) mode,<br>"0" = power-on enabled                                                                        |

| 15  | VND_IO_A   | I/O |                  | Module Vendor I/O A. Do Not Connect!                                                                                                          |

| 16  | VND_IO_B   | I/O |                  | Module Vendor I/O A. Do Not Connect!                                                                                                          |

| 17  | PRG_CNTL1  | 1   | LVCMOS<br>w/ PUR | Programmable Control 1 set over MDIO, MSA Default: TRXIC_RSTn, TX & RX ICs reset, "0": reset, "1" or NC: enabled = not used                   |

| 18  | PRG_CNTL2  |     | LVCMOS<br>w/ PUR | Programmable Control 2 set over MDIO, MSA Default: Hardware<br>Interlock LSB, "00": ≤3W, "01": ≤6W, "10": ≤9W, "11" or NC: ≤12W = not<br>used |

| 19  | PRG_CNTL3  | I   | LVCMOS<br>w/ PUR | Programmable Control 2 set over MDIO, MSA Default: Hardware<br>Interlock LSB, "00": ≤3W, "01": ≤6W, "10": ≤9W, "11" or NC: ≤12W = not<br>used |

| 20  | PRG_ALRM1  | 0   | LVCMOS           | Programmable Alarm 1 set over MDIO, MSA Default: HIPWR_ON, "1":<br>module power up completed, "0": module not high powered up                 |

| 21  | PRG_ALRM2  | 0   | LVCMOS           | Programmable Alarm 2 set over MDIO, MSA Default: MOD_READY, "1":<br>Ready, "0": not Ready.                                                    |

| 22  | PRG_ALRM3  | 0   | LVCMOS           | Programmable Alarm 3 set over MDIO, MSA Default: MOD_FAULT, fault detected, "1": Fault, "0": No Fault                                         |

| 23  | GND        |     |                  |                                                                                                                                               |

| 24  | TX_DIS     | I   | LVCMOS<br>w/ PUR | Transmitter Disable for all lanes, "1" or NC = transmitter disabled, "0" = transmitter enabled                                                |

| 25  | RX_LOS     | 0   | LVCMOS           | Receiver Loss of Optical Signal, "1": low optical signal, "0": normal condition                                                               |

| 26  | MOD_LOPWR  | I   | LVCMOS<br>w/ PUR | Module Low Power Mode. "1" or NC: module in low power (safe) mode,<br>"0": power-on enabled                                                   |

| 27  | MOD_ABS    | 0   | GND              | Module Absent. "1" or NC: module absent, "0": module present, Pull Up<br>Resistor on Host                                                     |

| 28  | MOD_RSTn   | I   | LVCMOS<br>w/ PDR | Module Reset. "0" resets the module, "1" or NC = module enabled, Pull<br>Down Resistor in Module                                              |

| 29  | GLB_ALRMn  | 0   | LVCMOS           | Global Alarm. "0": alarm condition in any MDIO Alarm register, "1": no alarm condition, Open Drain, Pull Up Resistor on Host                  |

|     |            |     |                  |                                                                                                                                               |

| 31 | MDC        | 1   | 1.2VCMOS | Management Data Clock (electrical specs as per IEEE Std 802.3ae-2008 and ba-2010)                   |

|----|------------|-----|----------|-----------------------------------------------------------------------------------------------------|

| 32 | MDIO       | I/O | 1.2VCMOS | Management Data I/O bi-directional data (electrical specs as per IEEE Std 802.3ae-2008 and ba-2010) |

| 33 | PRTADR0    | 1   | 1.2VCMOS | MDIO Physical Port address bit 0                                                                    |

| 34 | PRTADR1    | 1   | 1.2VCMOS | MDIO Physical Port address bit 1                                                                    |

| 35 | PRTADR2    | 1   | 1.2VCMOS | MDIO Physical Port address bit 2                                                                    |

| 36 | VND_IO_C   | I/O |          | Module Vendor I/O C. Do Not Connect!                                                                |

| 37 | VND_IO_D   | I/O |          | Module Vendor I/O D. Do Not Connect!                                                                |

| 38 | VND_IO_E   | I/O |          | Module Vendor I/O E. Do Not Connect!                                                                |

| 39 | 3.3V_GND   |     |          |                                                                                                     |

| 40 | 3.3V_GND   |     |          |                                                                                                     |

| 41 | 3.3V       |     |          | 3.3V Module Supply Voltage                                                                          |

| 42 | 3.3V       |     |          | 3.3V Module Supply Voltage                                                                          |

| 43 | 3.3V       |     |          | 3.3V Module Supply Voltage                                                                          |

| 44 | 3.3V       |     |          | 3.3V Module Supply Voltage                                                                          |

| 45 | 3.3V_GND   |     |          |                                                                                                     |

| 46 | 3.3V_GND   |     |          |                                                                                                     |

| 47 | N.C        |     |          | No Connect                                                                                          |

| 48 | N.C        |     |          |                                                                                                     |

| 49 | GND        |     |          |                                                                                                     |

| 50 | (RX_MCLKn) | 0   | CML      | For optical waveform testing. Not for normal use.                                                   |

| 51 | (RX_MCLKp) | 0   | CML      | For optical waveform testing. Not for normal use.                                                   |

| 52 | GND        |     |          |                                                                                                     |

| 53 | GND        |     |          |                                                                                                     |

| 54 | N.C.       |     |          |                                                                                                     |

| 55 | N.C.       |     |          |                                                                                                     |

| 56 | GND        |     |          |                                                                                                     |

| 57 | RX0p       |     |          | 25 Gbps receiver data; Lane 0                                                                       |

| 58 | RX0n       |     |          | 25 Gbps receiver data bar; Lane 0                                                                   |

| 59 | GND        |     |          |                                                                                                     |

| 60 | RX1p       |     |          | 25 Gbps receiver data; Lane 1                                                                       |

| 61 | RX1n       |     |          | 25 Gbps receiver data bar; Lane 1                                                                   |

| 62 | GND        |     |          |                                                                                                     |

| 63 | N.C.       |     |          |                                                                                                     |

| 64 | N.C.       |     |          |                                                                                                     |

| 65 | GND        |     |          |                                                                                                     |

| 66 | N.C.       |     |          |                                                                                                     |

| 67 | N.C.       |     |          |                                                                                                     |

| 68 | GND        |     |          |                                                                                                     |

| 69 | RX2p       |     |          | 25 Gbps receiver data; Lane 2                                                                       |

| 70 | RX2n       |     |          | 25 Gbps receiver data bar; Lane 2                                                                   |

| 71 | GND        |     |          |                                                                                                     |

| 72 | RX3р       |     |          | 25 Gbps receiver data; Lane 3                                                                       |

| 73  | RX3n      |     | 25 Gbps receiver data bar; Lane 3    |

|-----|-----------|-----|--------------------------------------|

| 74  | GND       |     |                                      |

| 75  | N.C.      |     |                                      |

| 76  | N.C.      |     |                                      |

| 77  | GND       |     |                                      |

| 78  | (REFCLKp) | CML | Module reference clock. No connect.  |

| 79  | (REFCLKn) | CML | Module reference clock. No connect.  |

| 80  | GND       |     |                                      |

| 81  | N.C.      |     |                                      |

| 82  | N.C.      |     |                                      |

| 83  | GND       |     |                                      |

| 84  | ТХ0р      |     | 25 Gbps transmitter data; Lane 0     |

| 85  | TX0n      |     | 25 Gbps transmitter data bar; Lane 0 |

| 86  | GND       |     |                                      |

| 87  | TX1p      |     | 25 Gbps transmitter data; Lane 1     |

| 88  | TX1n      |     | 25 Gbps transmitter data bar; Lane 1 |

| 89  | GND       |     |                                      |

| 90  | N.C.      |     |                                      |

| 91  | N.C.      |     |                                      |

| 92  | GND       |     |                                      |

| 93  | N.C.      |     |                                      |

| 94  | N.C.      |     |                                      |

| 95  | GND       |     |                                      |

| 96  | ТХ2р      |     | 25 Gbps transmitter data; Lane 2     |

| 97  | TX2n      |     | 25 Gbps transmitter data bar; Lane 2 |

| 98  | GND       |     |                                      |

| 99  | ТХ3р      |     | 25 Gbps transmitter data; Lane 3     |

| 100 | TX3n      |     | 25 Gbps transmitter data bar; Lane 3 |

| 101 | GND       |     |                                      |

| 102 | N.C.      |     |                                      |

| 103 | N.C.      |     |                                      |

| 104 | GND       |     |                                      |

## **Hardware Control Pins**

The CFP2 Module support real-time control functions via hardware pins, listed in the following.

| Pin | Symbol     | Description                                                                              | I/O | Logic                                      | Н                                      | Ļ      | Pull-up/down       |

|-----|------------|------------------------------------------------------------------------------------------|-----|--------------------------------------------|----------------------------------------|--------|--------------------|

| 17  | PRG_CNTL1  | Programmable Control 1 MSA De-<br>fault: TRXIC_RS Tn, TX&RX ICs reset,<br>"0": reset;"1" | I   | 3.3V LVCMOS                                | per CFP MSA<br>Management<br>Interface |        | Pull-Up Note1      |

| 18  | PRG_CNTL2  | Programmable Control 2 MSA De-<br>fault: Hardware Interlock LSB                          | I   | 3.3V LVCMOS                                | Specification                          |        | Pull-Up Note1      |

| 19  | PRG_CNTL3  | Programmable Control 3 MSA De-<br>fault: Hardware Interlock MSB                          | I   | 3.3V LVCMOS                                |                                        |        | Pull-Up Note1      |

| 26  | MOD_LOPW R | Module Low Power Mode                                                                    | 1   | 3.3V LVCMOS<br>Low Power<br>Enable Pull-Up | Low Power                              | Enable | Pull-Up Note1      |

| 28  | MOD_RSTn   | Module Reset (Invert)                                                                    | I   | 3.3V LVCMOS                                | Enable                                 | Reset  | Pull-Down<br>Note2 |

## Notes:

- 1. Pull-Up resistor (4.7KOhm to 10 KOhm) is located within the CFP2 module

- 2. Pull-Down resistor (4.7KOhm to 10 kOhm) is located within the CFP2 module

## **Hardware Alarm Pins**

The CFP2 Module supports alarm hardware pins listed in the following

| Pin | Symbol     | Description                                                                     | I/O | Logic       | Н                       | L       | Pull-up/down       |

|-----|------------|---------------------------------------------------------------------------------|-----|-------------|-------------------------|---------|--------------------|

| 20  | PRG_ALR M1 | Programmable Alarm 1 MSA<br>Default: HIPWR_ON                                   | 0   | 3.3V LVCMOS | Active High<br>per MDIO |         |                    |

| 21  | PRG_ALR M2 | Programmable Alarm 2 MSA<br>default: MOD_READY, Ready State<br>has been reached | 0   | 3.3V LVCMOS | document                |         |                    |

| 22  | PRG_ALR M3 | Programmable Alarm 3<br>MSA Default: MOD_FAULT                                  | 0   | 3.3V LVCMOS |                         |         |                    |

| 27  | MOD_ABS    | Module Absent                                                                   | 0   | 3.3V LVCMOS | Absent                  | Present | Pull-Down<br>Note1 |

| 25  | RX_LOS     | Receiver Loss of Signa                                                          | 0   | 3.3V LVCMOS | Loss of Signal          | ОК      |                    |

## Note:

1. Pull-Down resistor (<1000hm) is located within the CFP2 module. Pull-up should be located on the host

## **CFP2** Lane Assignment

| Lane | Center Frequency | Center Wavelength | Wavelength Range      |

|------|------------------|-------------------|-----------------------|

| LO   | 231.4 THz        | 1295.56 nm        | 1294.53 to 1296.59 nm |

| L1   | 230.6 THz        | 1300.05 nm        | 1299.02 to 1301.09 nm |

| L2   | 229.8 THz        | 1304.58 nm        | 1303.54 to 1305.63 nm |

| L3   | 229.0 THz        | 1309.14 nm        | 1308.09 to 1310.19 nm |

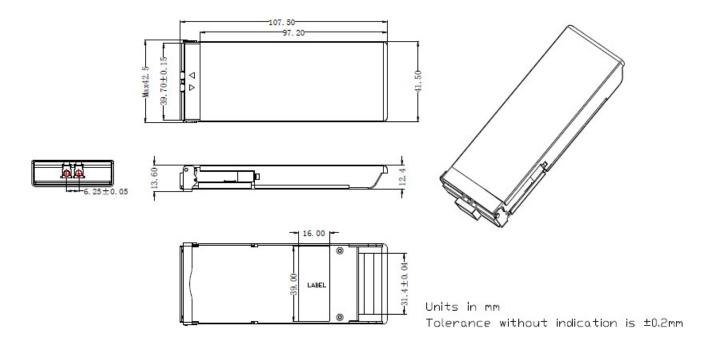

# **Mechanical Specifications**

## About AddOn Networks

In 1999, AddOn Networks entered the market with a single product. Our founders fulfilled a severe shortage for compatible, cost-effective optical transceivers that compete at the same performance levels as leading OEM manufacturers. Adhering to the idea of redefining service and product quality not previously had in the fiber optic networking industry, AddOn invested resources in solution design, production, fulfillment, and global support.

Combining one of the most extensive and stringent testing processes in the industry, an exceptional free tech support center, and a consistent roll-out of innovative technologies, AddOn has continually set industry standards of quality and reliability throughout its history.

Reliability is the cornerstone of any optical fiber network and is in engrained in AddOn's DNA. It has played a key role in nurturing the long-term relationships developed over the years with customers. AddOn remains committed to exceeding industry standards with certifications from ranging from NEBS Level 3 to ISO 9001:2005 with every new development while maintaining the signature reliability of its products.

### **U.S. Headquarters**

Email: sales@addonnetworks.com

Telephone: +1 877.292.1701

Fax: 949.266.9273

#### **Europe Headquarters**

Email: salessupportemea@addonnetworks.com

Telephone: +44 1285 842070